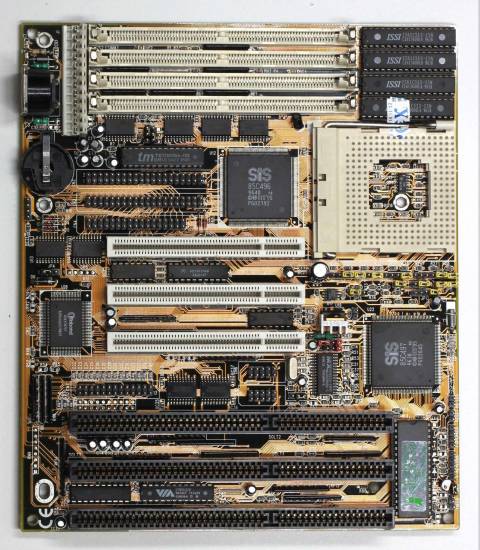

Lucky Star LS-486E Rev:C1/C2 (SIO with TTL chips)

25MHz33MHz40MHz50MHz

Baby AT (max 220 x 330 mm)

220mm x 190mm

128KB256KB512KB

128MB

72-pin FPM72-pin EDO

- Acorp <unknown>

1x

AT Keyboard

1x

Floppy interface

2x

IDE interface

1x

Parallel

2x

Serial

3x

16-bit ISA

3x

32-bit PCI

Rev C1 uses thru hole TTL chips near the LPT header, while rev C2 has surface mount TTL chips. There are versions that support EDO memory, not all of them do, this depends on the revision of the chipset.

512KB cache configuration:

- JP1: 1-2

- JP2: 2-3

- JP3 [factory hardwired to 2-3]: 1-2

Last updated 2025-12-11T08:09:57Z

Board info score is 9.6/10

-> Chipset part

-> Clock Synth / PLL

-> Human Interface

-> Signal transmitter/receiver

-> Super I/O

Award - 2 entries

POST string

Note

Core Ver.

BIOS Ver.

Logs

POST string

03/14/96-SiS-496-497/A/B-2A4IBL13C-00

Note

Core version

4.51G

BIOS version

Logs

Version

OS support

Arch

Size

Filename

Version

OS support

Arch

x86

Size

Empty

Filename

Version

OS support

Arch

x86

Size

97.9KB

Filename

Release date

File

Logs

Chip

Release date

File

Logs

Chip

Release date

2009-10

File

Logs

Chip

Release date

2013-04

File

Logs

Chip

Release date

2004-11

File

Logs

Chip

Release date

2025-10

File

Logs

Chip

Release date

2002-10-20

File

Logs

Chip

Release date

2006-01

File

Logs

Chip

Release date

2002-10-20

File

Logs

Family

Release date

File

Logs

Disclaimer

The info found in this page might not be entirely correct. Check out this guide to learn how you can improve it.

Image 1 of 6 (computerguy096)

Image 1 of 6 (computerguy096)

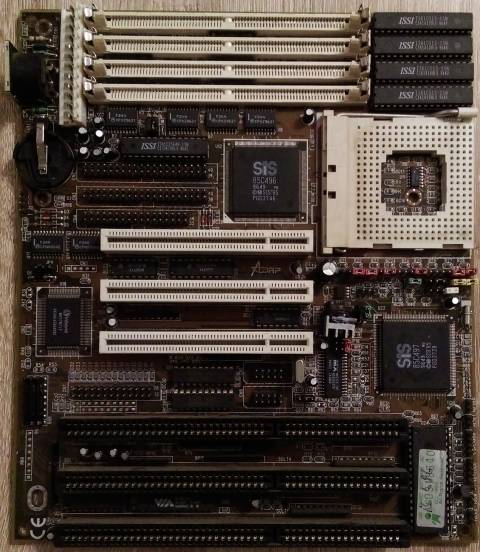

Image 2 of 6 (computerguy096)

Image 2 of 6 (computerguy096)

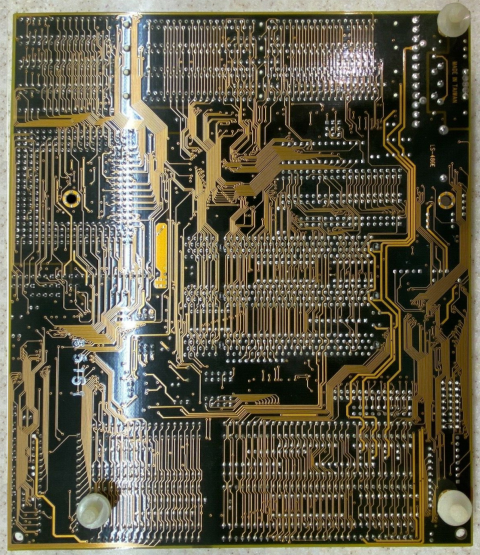

Image 3 of 6 (BreakPoint)

Image 3 of 6 (BreakPoint)

Image 4 of 6 (rad)

Image 4 of 6 (rad)

Image 5 of 6

Image 5 of 6

Image 6 of 6

Image 6 of 6