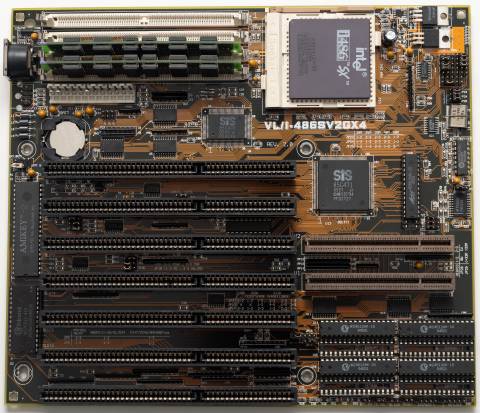

ASUS VL/I-486SV2GX4 Rev 2.0

20MHz25MHz33MHz40MHz50MHz

Baby AT (max 220 x 330 mm)

220mm x 257mm

128KB256KB512KB1MB

64MB

72-pin FPM

1x

AT Keyboard

1x

PS/2 mouse

7x

16-bit ISA

2x

32-bit VLB

The BIOS update (SV2G4fix.bin) fixes an issue from the latest BIOS (SV2G4021) in which the system does not properly set register 72h to TAG mode 7+1 when using write-back L2 cache. Without this, write back scores are worse than write through scores. After the BIOS fix, L2 mode write-back cache should be slightly faster than L2 write-through mode.

Last updated 2025-12-28T17:28:49Z

Board info score is 9.1/10

-> Chipset part

Award - 10 entries

POST string

Note

Core Ver.

BIOS Ver.

Logs

POST string

11/17/97-SIS-85C471-I486SV2GC-00

Note

Rev 1.7

Core version

4.51G

BIOS version

Logs

POST string

11/03/95-SIS-85C471-I486SV2G-00

Note

Rev 2.0, 2.1

Core version

4.50G

BIOS version

Logs

POST string

11/19/97-SIS-85C471-I486SV2GC-00

Note

BETA

Core version

4.51G

BIOS version

Logs

POST string

11/19/97-SIS-85C471-I486SV2GC-00

Note

modded, write-back L2 fix

Core version

4.51G

BIOS version

Logs

POST string

08/22/95-SIS-85C471-I486SV2G-00

Note

Rev 2.0, 2.1

Core version

4.50G

BIOS version

Logs

POST string

04/26/94-SIS-85C471-I486SV2G-00

Note

Dumped, came on Rev 1.7

Core version

4.50G

BIOS version

Logs

Release date

File

Logs

Chip

Release date

File

Logs

Family

Release date

File

Logs

Disclaimer

The info found in this page might not be entirely correct. Check out this guide to learn how you can improve it.

Image 1 of 10 (Microhouse)

Image 1 of 10 (Microhouse)

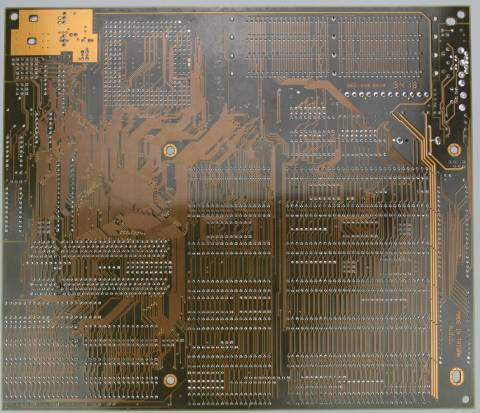

Image 2 of 10 (MMaximus)

Image 2 of 10 (MMaximus)

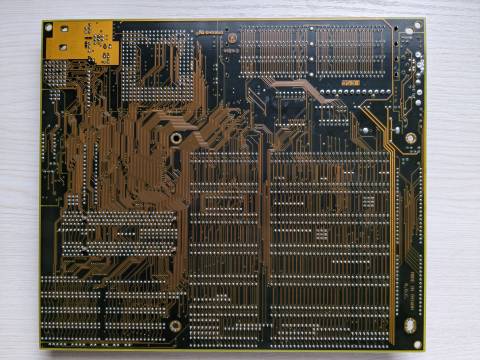

Image 3 of 10 (Clous)

Image 3 of 10 (Clous)

Image 4 of 10 (dataino.it)

Image 4 of 10 (dataino.it)

Image 5 of 10 (chrisNova777)

Image 5 of 10 (chrisNova777)

Image 6 of 10 (ChrisR3tro)

Image 6 of 10 (ChrisR3tro)

Image 7 of 10 (ChrisR3tro)

Image 7 of 10 (ChrisR3tro)

Image 8 of 10 (Clous)

Image 8 of 10 (Clous)

Image 9 of 10 (dataino.it)

Image 9 of 10 (dataino.it)

Image 10 of 10 (ChrisR3tro)

Image 10 of 10 (ChrisR3tro)